#### Lecture Notes in Computer Science

3308

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

**David Hutchison**

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

New York University, NY, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Jim Davies Wolfram Schulte Mike Barnett (Eds.)

# Formal Methods and Software Engineering

6th International Conference on Formal Engineering Methods, ICFEM 2004 Seattle, WA, USA, November 8-12, 2004 Proceedings

#### Volume Editors

Jim Davies University of Oxford, Software Engineering Programme Wolfson Building, Parks Road, Oxford OX1 3QD, UK E-mail: jim.davies@comlab.ox.ac.uk

Wolfram Schulte

Mike Barnett

Microsoft Research

One Microsoft Way, Cedar Court 113/4048, Redmond, WA 98052-6399, USA

E-mail: {schulte, mbarnett}@microsoft.com

Library of Congress Control Number: 2004114617

CR Subject Classification (1998): D.2.4, D.2, D.3, F.3

ISSN 0302-9743 ISBN 3-540-23841-7 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springeronline.com

© Springer-Verlag Berlin Heidelberg 2004 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 11348801 06/3142 5 4 3 2 1 0

#### **Preface**

Formal engineering methods are changing the way that software systems are developed. With language and tool support, they are being used for automatic code generation, and for the automatic abstraction and checking of implementations. In the future, they will be used at every stage of development: requirements, specification, design, implementation, testing, and documentation.

The ICFEM series of conferences aims to bring together those interested in the application of formal engineering methods to computer systems. Researchers and practitioners, from industry, academia, and government, are encouraged to attend, and to help advance the state of the art. Authors are strongly encouraged to make their ideas as accessible as possible, and there is a clear emphasis upon work that promises to bring practical, tangible benefit: reports of case studies should have a conceptual message, theory papers should have a clear link to application, and papers describing tools should have an account of results.

ICFEM 2004 was the sixth conference in the series, and the first to be held in North America. Previous conferences were held in Singapore, China, UK, Australia, and Japan. The Programme Committee received 110 papers and selected 30 for presentation. The final versions of those papers are included here, together with 2-page abstracts for the 5 accepted tutorials, and shorter abstracts for the 4 invited talks.

We would like to thank: Dines Bjørner, for his work in organizing speakers and sponsors; Jin Song Dong and Jim Woodcock, for an excellent handover from ICFEM 2003; Joxan Jaffar, J Strother Moore, Peter Neumann, and Amitabh Srivastava, for agreeing to address the conference; the authors, for submitting their work; the Programme Committee, and their colleagues, for their reviews; and Springer, for their help with publication.

ICFEM 2004 was organized by Microsoft Research in Seattle, with additional support and sponsorship from the University of Oxford, the United Nations University, Formal Methods Europe, NASA, and ORA Canada.

November 2004 Jim Davies

Wolfram Schulte

Mike Barnett

#### Organizing Committee

#### Conference Committee

Mike Barnett (Microsoft Research, USA)

Local Organization

Dines Bjørner (National University of Singapore, Singapore)

Conference Chair

Jim Davies (University of Oxford, UK)

Programme Co-chair

Wolfram Schulte (Microsoft Research, USA)

Programme Co-chair

Hongjun Zheng (Semantics Design, USA)

Workshops and Tutorials Chair

#### Sponsors

Microsoft Research

www.research.microsoft.com

Oxford University Software Engineering Programme

www.softeng.ox.ac.uk

United Nations University-International Institute for Software Technology

www.iist.unu.edu

Formal Methods Europe (FME)

www.fmeurope.org

NASA-JPL Laboratory for Reliable Software

eis.jpl.nasa.gov/lars/

ORA Canada

www.ora.on.ca

#### Steering Committee

Keijiro Araki (Kyushu University, Japan)

Jin Song Dong (National University of Singapore, Singapore)

Chris George (United Nations University, Macau)

Jifeng He (Chair) (IIST, United Nations University, Macau)

Mike Hinchey (NASA, USA)

Shaoying Liu (Hosei University, Japan)

John McDermid (University of York, UK)

Tetsuo Tamai (University of Tokyo, Japan)

Jim Woodcock (University of York, UK)

#### Programme Committee

Adnan Aziz (University of Texas, USA)

Richard Banach (University of Manchester, UK)

Egon Börger (University of Pisa, Italy)

Jonathan Bowen (London South Bank University, UK)

Manfred Broy (University of Munich, Germany)

Michael Butler (University of Southampton, UK)

Ana Cavalcanti (University of Kent, UK)

Dan Craigen (ORA, Canada)

Jin Song Dong (National University of Singapore, Singapore)

Matthew Dwyer (Kansas State University, USA)

John Fitzgerald (University of Newcastle upon Tyne, UK)

David Garlan (Carnegie Mellon University, Pittsburgh, USA)

Thomas Jensen (IRISA/CNRS Campus de Beaulieu, Rennes, France)

Jim Larus (Microsoft Research, USA)

Mark Lawford (McMaster University, Canada)

Huimin Lin (Chinese Academy of Sciences, Beijing, China)

Peter Lindsay (University of Queensland, Australia)

Shaoying Liu (Hosei University, Japan)

Zhiming Liu (United Nations University, Macau SAR, China)

Brendan Mahony (Department of Defence, Australia)

Marc Frappier (Université de Sherbrooke, Québec, Canada)

William Bradley Martin (National Security Agency, USA)

David Notkin (University of Washington, USA)

Jeff Offutt (George Mason University, USA)

Harald Ruess (Computer Science Laboratory, SRI, USA)

Augusto Sampaio (Universidade Federal de Pernambuco, Brazil)

Thomas Santen (Technical University of Berlin, Germany)

Doug Smith (Kestrel Institute, USA)

Graeme Smith (University of Queensland, Australia)

Paul A. Swatman (University of South Australia, Australia)

Sofiene Tahar (Concordia University, Canada)

T.H. Tse (Hong Kong University, Hong Kong)

Yi Wang (Uppsala University, Sweden)

Farn Wang (National Taiwan University, Taiwan)

Jeannette Wing (Carnegie Mellon University, USA)

Jim Woodcock (University of York, UK)

#### Reviewers

Amr Abdel-Hamid; Isaam Al-azzoni; Adnan Aziz; Richard Banach; Andreas Bauer; Jounaidi Ben Hassen; Egon Börger; Jonathan Bowen; Peter Braun; Manfred Broy; Michael Butler; Colin Campbell; Ana Cavalcanti; Alessandra Cavarra; Antonio Cerone; Yifeng Chen; Corina Cirstea; David Clark; Dan Craigen; Charles Crichton; Jim Davies; Roger Duke; Bruno Dutertre; Matthew Dwyer; Pao-Ann Eric Hsiung; Yuan Fang Li; Bill Farmer; William M. Farmer; Carla Ferreira; Colin Fidge; John Fitzgerald; Marc Frappier; Jorn Freiheit; David Garlan; Amjad Gawanmeh; Frederic Gervais; Jeremy Gibbons; Uwe Glaesser; Andy Gravell; Wolfgang Grieskamp; Ali Habibi; John Hakansson; Steve Harris; Jifeng He; Maritta Heisel; Steffen Helke; Matthew Hennessy; Xiayong Hu; Geng-Dian Huang; Chung-Yang Ric Huang; Van Hung Dang; Jiale Huo; Cornelia P. Inggs; Jan Jürjens; Bart Jacobs; Thomas Jensen; Thierry Jeron; Zhi Jin; Wolfram Kahl; Soon-Kyeong Kim; Soon Kyeong Kim; Leonid Kof; Pushmeet Kohli; Pavel Krcal; Sv-Yen Kuo; Rom Langerak; James Larus; Mark Lawford; Ryan Leduc; Karl Lermer; Guangyuan Li; Xiaoshan Li; Huimin Lin; Peter Lindsay; Shaoying Liu; Zhiming Liu; Quan Long; Marcio Lopes Cornelio; Dorel Lucanu; Anthony MacDonald; Brendan Mahony; William Bradley Martin; Jim McCarthy; M. Meisinger; Yassine Mokhtari; Leonid Mokrushin; Alexandre Mota; Muan Yong Ng; Sidney Nogueira; David Notkin; Jeff Offutt; Chun Ouyang; Hong Pan; Jun Pang; Paul Pettersson; Mike Poppleton; Steven Postma; Stephane Lo Presti; Wolfgang Reisig; Abdolbaghi Rezazadeh; River; Harald Ruess; Heinrich Rust; Vlad Rusu; Augusto Sampaio; Thomas Santen; Renate Schmidt; Wolfram Schulte; Thorsten Schutt; Dirk Seifert; Laura Semini; Adnan Sherif; Benjamin Sigonneau; Carlo Simon; Andrew Simpson; Doug Smith; Graeme Smith; Doug Smith; Colin Snook; Jin Song Dong; Maria Sorea; Mark Staples; Jun Sun; Paul A. Swatman; Sofiene Tahar; J.P. Talpin; Rodrigo Teixeira Ramos; Nikolai Tillmann; T.H. Tse; Phillip J. Turner; Margus Veanes; S. Vogel; Philip Wadler; Farn Wang; Bow-Yaw Wang; Alan Wassyng; Jun Wei; Guido Wimmel; Jeannette Wing; Kirsten Winter; Jim Woodcock; Wang Yi; Fang Yu; Mohamed Zaki; Wenhui Zhang; Guangquan Zhang; Ning Zhang; Riley Zheng; Xiaocong Zhou; Jeff Zucker

#### **Table of Contents**

#### **Tutorials**

| Model-Based Development: Combining Engineering Approaches and Formal Techniques                                                     |    |

|-------------------------------------------------------------------------------------------------------------------------------------|----|

| Bernhard Schätz                                                                                                                     | 1  |

| Tutorial on the RAISE Language, Method and Tools  Chris George                                                                      | 3  |

| Model-Based Testing with Spec#  Jonathan Jacky                                                                                      | 5  |

| Formal Engineering for Industrial Software Development – An Introduction to the SOFL Specification Language and Method Shaoying Liu | 7  |

| Tutorial: Software Model Checking  Edmund Clarke, Daniel Kroening                                                                   | 9  |

| Invited Talks                                                                                                                       |    |

| Engineering Quality Software  Amitabh Srivastava                                                                                    | 11 |

| When Can Formal Methods Make a Real Difference?  Peter G. Neumann                                                                   | 12 |

| On the Adoption of Formal Methods by Industry: The ACL2 Experience $J$ Strother Moore                                               | 13 |

| A CLP Approach to Modelling Systems  Joxan Jaffar                                                                                   | 14 |

| Full Papers                                                                                                                         |    |

| Multi-prover Verification of C Programs  Jean-Christophe Filliâtre, Claude Marché                                                   | 15 |

| Memory-Model-Sensitive Data Race Analysis  Yue Yang, Ganesh Gopalakrishnan, Gary Lindstrom                                          | 30 |

| Formal Models for Web Navigations with Session Control and Browser                                                                  |    |

| Cache  Jessica Chen, Xiaoshan Zhao                                                                                                  | 46 |

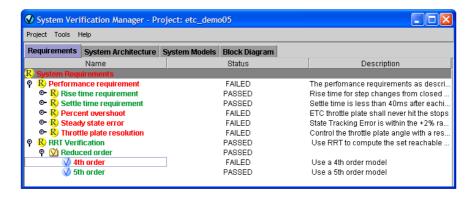

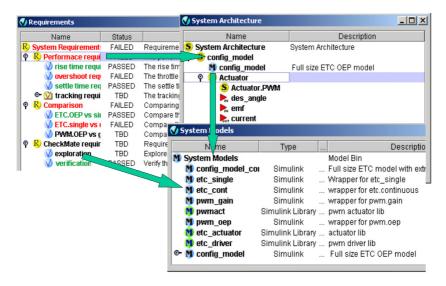

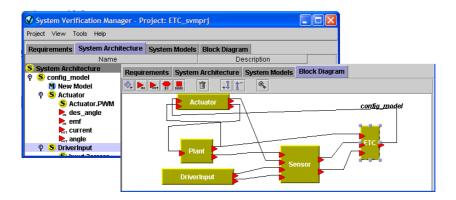

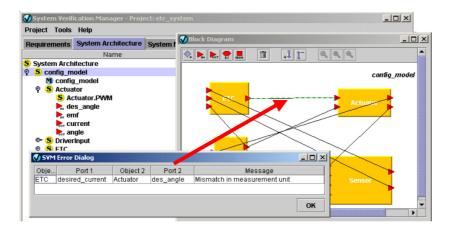

| Managing Verification Activities Using SVM  Bill Aldrich, Ansgar Fehnker, Peter H. Feiler, Zhi Han,  Bruce H. Krogh, Eric Lim, Shiva Sivashankar | 61  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A General Model for Reachability Testing of Concurrent Programs  Richard H. Carver, Yu Lei                                                       | 76  |

| A Knowledge Based Analysis of Cache Coherence  Kai Baukus, Ron van der Meyden                                                                    | 99  |

| A Propositional Logic-Based Method for Verification of Feature Models Wei Zhang, Haiyan Zhao, Hong Mei                                           | 115 |

| Deriving Probabilistic Semantics Via the 'Weakest Completion'  He Jifeng, Carroll Morgan, Annabelle McIver                                       | 131 |

| CSP Representation of Game Semantics for Second-Order Idealized Algol  Aleksandar Dimovski, Ranko Lazić                                          | 146 |

| An Equational Calculus for Alloy  Marcelo F. Frias, Carlos G. López Pombo, Nazareno M. Aguirre                                                   | 162 |

| Guiding Spin Simulation  Nicolae Goga, Judi Romijn                                                                                               | 176 |

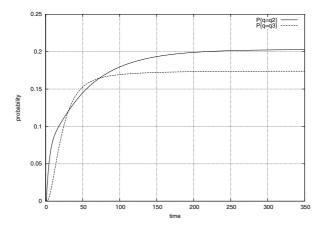

| Linear Inequality LTL ( <i>iLTL</i> ): A Model Checker for Discrete Time Markov Chains  YoungMin Kwon, Gul Agha                                  | 194 |

| Software Model Checking Using Linear Constraints  Alessandro Armando, Claudio Castellini, Jacopo Mantovani                                       | 209 |

| Counterexample Guided Abstraction Refinement Via Program Execution  Daniel Kroening, Alex Groce, Edmund Clarke                                   | 224 |

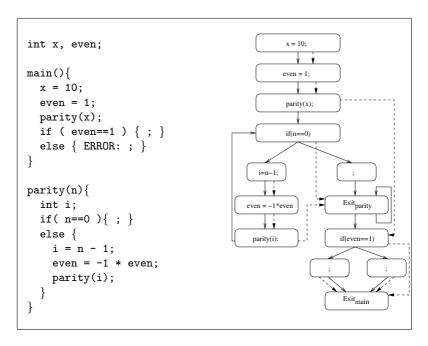

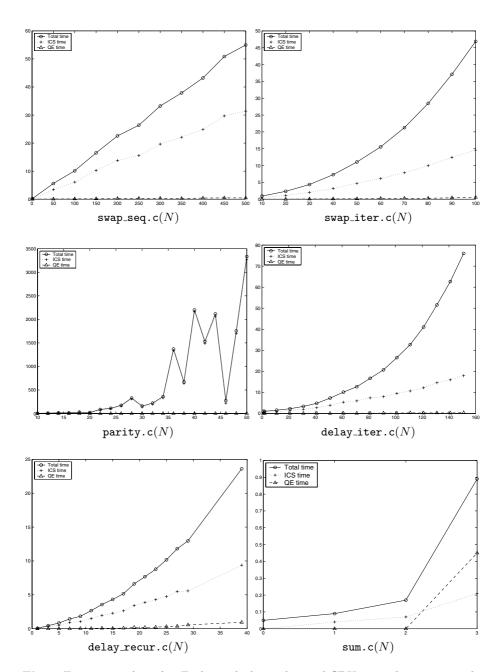

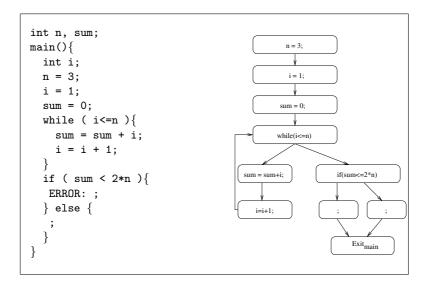

| Faster Analysis of Formal Specifications Fabrice Bouquet, Bruno Legeard, Mark Utting, Nicolas Vacelet                                            | 239 |

| Bridging Refinement of Interface Automata to Forward Simulation of I/O Automata  Yanjun Wen, Ji Wang, Zhichang Qi                                | 259 |

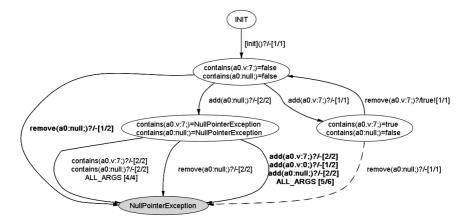

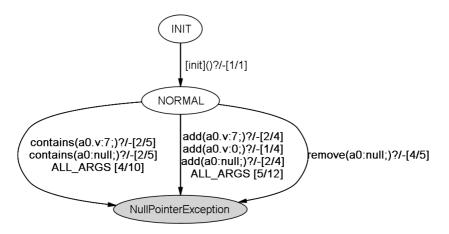

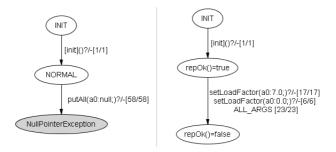

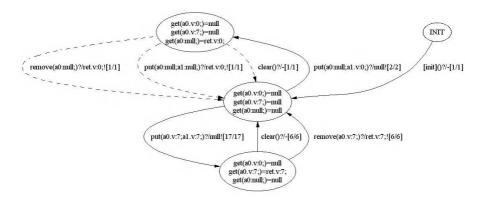

| Learning to Verify Safety Properties  Abhay Vardhan, Koushik Sen, Mahesh Viswanathan, Gul Agha                                                   | 274 |

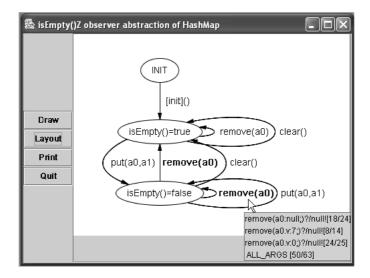

| Automatic Extraction of Object-Oriented Observer Abstractions from Unit-Test Executions  Tao Xie. David Notkin                                   | 290 |

| Table of Contents                                                                                                                           | XIII |

|---------------------------------------------------------------------------------------------------------------------------------------------|------|

| A Specification-Based Approach to Testing Polymorphic Attributes  Ling Liu, Huaikou Miao                                                    | 306  |

| From Circus to JCSP  Marcel Oliveira, Ana Cavalcanti                                                                                        | 320  |

| An Approach to Preserve Protocol Consistency and Executability  Across Updates  Mahadevan Subramaniam, Parvathi Chundi                      | 341  |

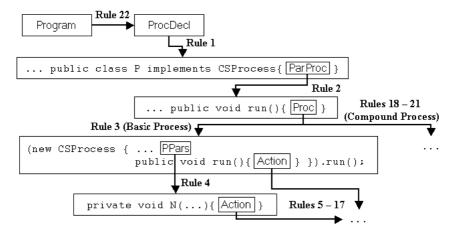

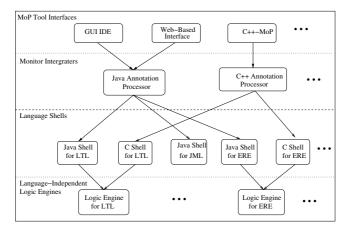

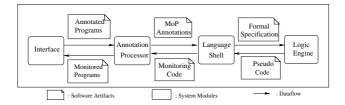

| A Formal Monitoring-Based Framework for Software Development and Analysis  Feng Chen, Marcelo D'Amorim, Grigore Roşu                        | 357  |

| Verifying a File System Implementation  Konstantine Arkoudas, Karen Zee, Viktor Kuncak, Martin Rinard                                       | 373  |

| Verifying the On-line Help System of SIEMENS Magnetic Resonance Tomographs Carsten Sinz, Wolfgang Küchlin                                   | 391  |

| Implementing Dynamic Aggregations of Abstract Machines in the B<br>Method<br>Nazareno Aguirre, Juan Bicarregui, Lucio Guzmán, Tom Maibaum   | 403  |

| Formal Proof from UML Models  Nuno Amálio, Susan Stepney, Fiona Polack                                                                      | 418  |

| Interactive Verification of UML State Machines  Michael Balser, Simon Bäumler, Alexander Knapp, Wolfgang Reif,  Andreas Thums               | 434  |

| Refinement of Actions for Real-Time Concurrent Systems with Causal Ambiguity  Mila Majster-Cederbaum, Jinzhao Wu, Houguang Yue, Naijun Zhan | 449  |

| From Durational Specifications to TLA Designs of Timed Automata  Yifeng Chen, Zhiming Liu                                                   | 464  |

| Timed Patterns: TCOZ to Timed Automata  Jin Song Dong, Ping Hao, Sheng Chao Qin, Jun Sun, Wang Yi                                           | 483  |

| Author Index                                                                                                                                | 499  |

#### Model-Based Development: Combining Engineering Approaches and Formal Techniques

#### Bernhard Schätz

Institut für Informatik, Technische Universität München, 80290 München, Germany

#### 1 Model-Based Development

In a nutshell, a model-based approach offers several benefits:

**Improved Product:** By moving away from an implementation biased view of a system, the developer can focus on the important issues of the product under development. This results in

- thinking in terms of the domain-specific conceptual model (state, interaction, etc.) instead of the coding level (objects, method calls, etc.)

- narrowing the gap between informal specification and formal specification (since, e.g., notions like mode, event, or communication, appear in the informal specifications as well as in the model)

- limiting the possibility of making mistakes while building models and refining them by ensuring consistency conditions (e.g. interface correctness, absence of undefined behavior)

**Improved Process:** Using a better structured product model helps to identify more defects earlier. Additionally, higher efficiency can be obtained by more CASE-supported process steps

- mechanizing conceptual consistency conditions, either guaranteed by construction (e.g., interface correctness) or checked automatically on demand (e.g., completeness of defined behavior)

- supporting semantical consistency conditions, either automatically (e.g., checking whether an EET can be performed by system), or interactively (e.g., by ensuring a safety condition of a system)

- enabling transformations of specification (e.g. inserting standard behavior for undefined situations), interactively carried out by the CASE tool.

The limit of model-based support is defined by the sophistication of the underlying model: by adding more domain-specific aspects, more advanced techniques can be offered (e.g., reliability analysis, schedule generation).

#### 2 Structured Development

Model-based development is all about adding the structuring and preciseness of formal approaches to the development process while being driven by the models of the application domain instead of mathematical formalisms.

J. Davies et al. (Eds.): ICFEM 2004, LNCS 3308, pp. 1–2, 2004.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2004

Thus it helps reducing the complexity of the development process by clearly focusing on specific issues and offering suitable, generally CASE-supported techniques tailored for each step of the development (see also [1]):

- **Step 1:** By linking informal requirements and the models of system and environment, we can check whether all informal requirements are covered or trace back from design to requirements; but most importantly, it helps to structure the requirements, get a better understanding, and identify open issues in the requirements.

- **Step 2:** By modeling the environment and its interface to the system, we get a precise understanding of how the system influences the environment and how the environment reacts. Especially important, we precisely state what properties of the environment we take for granted and which possibly faulty behavior we must tolerate to establish the required safety behavior.

- **Step 3:** By defining the abstract, possibly incomplete and non-deterministic behavior of the system, we describe a high-level initial design without already incorporating implementation details complicating the design or limiting further decision. Furthermore, we establish the basis for further analysis and development steps.

- **Step 4:** By analyzing the models of system and environment for their validity, we ensure their usefulness for the following steps; using simulation or conceptual consistency checks, we identify open issues like unrealistic behavior of the environment, as well as undefined behavior of the system.

- Step 5: By using even stronger techniques we establish whether the defined behavior of the system ensures the expected behavior of the environment. Using formal verification, we show that the system guarantees the safety requirements of the environment assuming optimal circumstances; furthermore, using failure analysis, we show that also mean time requirements are met using quantitative assumptions about the environment.

- **Step 6:** By applying structural refinement, we add further design decisions concerning the architecture of a system by breaking it up into interacting sub-components. By adding behavior to each sub-component, we can make sure that the refined system implements the abstract one.

- **Step 7:** By restricting non-deterministic or undefined behavior, we add further design decisions concerning underspecified behavior of the introduced components, resulting in a more optimized reaction of the system while maintaining the overall functionality.

- **Step 8:** By checking the components of the system for possible undefined behavior we identify remaining open behavior to be resolved in the final implementation. By adding standard reactions for open behavior, we improve the robustness of the system against unexpected behavior.

#### References

B. Schätz. Mastering the Complexity of Embedded Systems - The AutoFocus Approach. In F. Kordon and M. Lemoine, editors, Formal Techniques for Embedded Distributed Systems: From Requirements to Detailed Design. Kluwer, 2004.

#### Tutorial on the RAISE Language, Method and Tools

Chris George

United Nations University, International Institute for Software Technology (UNU-IIST), Macao cwg@iist.unu.edu http://www.iist.unu/~cwg

Abstract. RAISE — Rigorous Approach to Industrial Software Engineering — was first developed in European collaborative projects during 1985-94. Since then a new set of free, open-source, portable tools has been developed, and a range of developments have been carried out. This tutorial introduces the language and method, and demonstrates the range of software life-cycle activities supported by the tools. These include generation of specifications from UML class diagrams, validation and verification of specifications, refinement, prototyping, execution of test cases, mutation testing, generation of documents, proof by means of translation to PVS, and generation of program code in C++ by translation. A comprehensive user guide is also available.

It is a common perception that "formal methods" are difficult to use, involve a lot of proof, are expensive, and are only applicable to small, critical problems. The aim of this tutorial is to introduce a formal technology that is easy to learn, need involve no proof at all, is cheap to apply, and is intended in particular to deal with large, not necessarily critical problems.

The RAISE method [1] is extreme in its basic simplicity: you write a specification and then you produce the implementation (if possible, automatically from the specification). You may for a particular project want to do more than this: you may decide you want to produce a more abstract specification first, and then a more concrete one, and then perhaps assert (and even prove) some relation, such as refinement, between them. But for many projects one specification is enough [2]. If you find graphical approaches useful, you can start by drawing a UML class diagram and generate the first specification from it.

What this simple picture of the method hides is the urgent need to validate the specification. Many discussions on formal methods assume the specification is correct, is what you want, and concentrate on verification, on showing that it is properly implemented. But all this is wasted if the specification is wrong. Mistakes made at the beginning of a project (and not quickly noticed) cause many problems, at best time and cost overruns, and at worst complete failure. So a major aim of the RAISE method, and of the tools that support it, is exploring and finding problems with the specification.

Concretely we can, with the tools:

- write large specifications in modules that we can analyse separately;

- generate and inspect "confidence conditions" that subtype conditions are not violated, pre-conditions are satisfied by function calls, cases are complete, etc.;

- translate and execute test cases that are recorded with the specification;

- assess the adequacy of test cases by means of specification mutation testing;

- generate high quality documents that include the specifications; and even, for more critical applications,

- prove confidence conditions, refinement, or other properties that we choose to assert

The RAISE Specification Language (RSL) [3] is a "wide-spectrum" language. It supports "algebraic" as well as "model-oriented" styles, and also includes applicative, imperative and concurrent features. It is modular, and therefore supports the writing of a very wide range of specifications.

Introductory information on the language and method is available in a variety of papers [4–6]. There is also an extension to RSL to deal with time [7].

The RAISE tool is open source, comes ready built for Windows, Linux and Sparc-Solaris, and can be built in any environment where you can compile C. There is also a comprehensive user guide [8].

The tutorial covers RSL, the method, the tools, and gives an example of a large system specified using RAISE.

#### References

- The RAISE Language Group. The RAISE Development Method. BCS Practitioner Series. Prentice Hall, 1995. Available from ftp://ftp.iist.unu.edu/pub/RAISE/method\_book.

- 2. Hung Dang Van, Chris George, Tomasz Janowski, and Richard Moore. Specification Case Studies in RAISE. FACIT. Springer-Verlag, 2002.

- 3. The RAISE Language Group. The RAISE Specification Language. BCS Practitioner Series. Prentice Hall, 1992. Available from Terma A/S. Contact jnp@terma.com.

- Chris George. A RAISE Tutorial. Technical Report 153, UNU-IIST, P.O.Box 3058, Macau, December 1998. Presented at the BRNS workshop Verification of Digital and Hybrid Systems at TIFR, Mumbai, India, 7–11 January 1999.

- 5. Chris George. Introduction to RAISE. Technical Report 249, UNU-IIST, P.O. Box 3058, Macau, April 2002.

- 6. Chris George and Anne E. Haxthausen. The Logic of the RAISE Specification Language. Computing and Informatics, 22(3–4), 2003.

- Chris George and Xia Yong. An Operational Semantics for Timed RAISE. Technical Report 149, UNU-IIST, P.O.Box 3058, Macau, November 1998. Presented at and published in the proceedings of FM'99, Toulouse, France, 20–24 September 1999, LNCS 1709, Springer-Verlag, 1999, pp. 1008–1027.

- 8. Chris George. RAISE Tools User Guide. Technical Report 227, UNU-IIST, P.O. Box 3058, Macau, February 2001. The tools are available from http://www.iist.unu.edu.

#### Model-Based Testing with Spec#

Jonathan Jacky

University of Washington, Seattle, USA

#### 1 Introduction

This half-day tutorial introduces model-based testing, using the Spec# modeling language and the Spec Explorer test tool.

We write a model program (an executable specification) in Spec# that models the implementation we wish to test. Then we use Spec Explorer to validate the model program, generate test suites from the model program, and execute conformance tests, using the model program again as the oracle.

#### 2 The Spec# Language

The Spec# language is a superset of C# with additional constructs for contracts. A contract is (part of) a specification expressed in the programming language itself. Spec# provides two kinds of contracts: declarative contracts and model programs.

#### 2.1 Declarative Contracts

A declarative contract is an assertion: a Boolean expression that describes a condition that should be true at certain times during program execution. Spec# provides several kinds of declarative contracts, including preconditions and post-conditions.

Each precondition and postcondition is associated with a method. A precondition is supposed to be true when execution enters its method. Preconditions often express requirements on method arguments. A postcondition should be true when its method exits. It expresses the intended result or effect of the method.

Spec# provides more Boolean operators (such as implication) and more kinds of Boolean expressions (such as quantified expressions) to make it easier to write expressive declarative contracts.

#### 2.2 Model Programs

It can be quite difficult to write postconditions that express exactly what is intended. It is often easier and clearer to write a program that demonstrates the intended effect. A program written for this purpose is a kind of contract. It is called an executable specification or a model program.

J. Davies et al. (Eds.): ICFEM 2004, LNCS 3308, pp. 5–6, 2004.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2004

In order to be useful, a model program must be shorter and clearer than the program it models. Spec# provides constructs that make this possible. In effect, Spec# is a very high level programming language. For example, it provides more collection types (sets, sequences, and maps) and expressions (comprehensions) that enable collections to be created and manipulated without coding loops, indices, or references.

#### 3 The Spec Explorer Tool

The Spec Explorer tool can investigate the properties of model programs written in Spec#, using a process called exploration which is similar to model checking. It can also generate test suites and perform conformance tests.

#### 3.1 Exploration

Exploration performs all possible executions of the model program (including all possible interleavings of operations), within a finite scope that is configured by the user. Exploration generates the graph of a finite (perhaps quite large) state machine which is a portion (an under-approximation) of the finite (but astronomically large) state machine that would be generated if the program could be explored completely (without any limitations on its scope). Each edge in the graph is a method invocation (including particular argument values).

Spec Explorer provides several ways for the user to limit exploration by configuring finite domains for each method argument, limitations on the sizes of data structures, equivalence classes on states (where only one representative state from each class will be explored), and various other stopping conditions.

Exploration can check safety properties by searching for unsafe states, and investigate liveness by searching for paths to goal states.

#### 3.2 Test Suite Generation

Spec Explorer can generate test suites by traversing the graph of the finite state machine. Different traversal algorithms achieve different coverage. For example, a postman tour achieves full link coverage.

#### 3.3 Conformance Testing

Spec Explorer can perform conformance tests. It includes a test harness that can execute generated test suites on the implementation and the model program in lockstep, using the model program as the oracle to check the implementation.

#### 4 References

For more information about the Spec# language and Spec Explorer tool consult the Foundations of Software Engineering web site at Microsoft Research:

http://research.microsoft.com/fse/

## Formal Engineering for Industrial Software Development – An Introduction to the SOFL Specification Language and Method

Shaoying Liu

Department of Computer Science,

Faculty of Computer and Information Sciences,

Hosei University, Tokyo, Japan

sliu@k.hosei.ac.jp

http://cis.k.hosei.ac.jp/~sliu/

Formal methods have been developed as a rigorous approach to computer systems development over last three decades, but have been facing challenges in fighting for industrial acceptance in general. Most commonly used formal methods do not offer comprehensible structuring mechanism for building complex systems; formal refinement is not sufficient to deal with real development situations; and formal verification requires high skills and is time-intensive, and is therefore expensive to be adopted by industry.

Having mentioned these challenges, we do not mean to suggest the denial of the advantages of formal methods in achieving preciseness and conciseness of software systems. In fact, our position is in favour of adopting formal methods, but emphasize that it must be employed in an appropriate manner that can significantly improve the rigor, comprehensibility, and the controllability of the commonly used software engineering methods and processes. To this end, we believe that it is important to improve the languages and techniques for constructing formal specifications, refining specifications, and verifying and validating specifications and programs.

One effective way to realize this goal is to provide a formal but practical specification language and method by properly integrating existing formal methods and informal or semi-formal methods commonly used in industry. Such a method should allow developers to systematically carry out software development using a comprehensible notation in a rigorous and controllable process. It should also offer a means for effective cooperation among different people within the same software project, such as managers, analysts, designers, programmers, and testers. Furthermore, perhaps the most important feature of such a method would be the tool supportability; that is, the method should be easily supported in depth.

On the basis of our intensive research and application experience over the last fifteen years, we have developed the SOFL specification language and method for software development [1,2,3], aiming to address these problems. As a specification language, SOFL integrates VDM-SL, Data Flow Diagrams, and Petri Nets to provide an intuitive, rigorous, and comprehensible formal notation for specifications at different levels. Compared to UML (Unified Modeling Language), SOFL provides a simpler but systematic mechanism for *precisely* defining the

functions of system units and their integration, and therefore avoids the difficulty in managing different kinds of diagrams and their consistency in UML. As a method, it combines structured methods and object-oriented methods, and advocates an transformational and evolutionary approach to constructing formal specifications from informal and then semi-formal specifications; it integrates the idea of formal proof and commonly used verification and validation techniques, such as testing and reviews, to offer rigorous but practical verification techniques.

After a brief description of the general principle of Formal Engineering Methods, this tutorial offers a systematic introduction to the SOFL specification language, method, process, and supporting tools. Specifically, the tutorial is divided into three parts. The first part includes the brief introduction to Formal Engineering Methods and the SOFL specification language. In particular, we will focus on the explanation of the idea of using the graphical notation, known as Condition Data Flow Diagram (or CDFD for short), to model the architecture of a system, while using the pre-post notation to define the functionality of processes occurring in CDFDs. The second part explains the SOFL method and process: how SOFL can be used to construct a formal specification by taking a three-step: informal, semi-formal, and formal specifications. It also explains how structured abstract design can be smoothly transformed into object-oriented detailed design and programs. Furthermore, the role of each form of these specifications in the entire software development process is also elaborated. Finally, the third part of the tutorial presents Rigorous Review and Specification Testing as two practical techniques for verification and validation of specifications, and demonstrates several tools we have built to support SOFL.

#### References

- [1] Shaoying Liu. Formal Engineering for Industrial Software Development Using the SOFL Method. Springer-Verlag, 2004.

- [2] Shaoying Liu, Jeff Offutt, Chris Ho-Stuart, Yong Sun, and Mitsuru Ohba. SOFL: A Formal Engineering Methodology for Industrial Applications. *IEEE Transactions on Software Engineering*, 24(1):337–344, January 1998. Special Issue on Formal Methods.

- [3] Shaoying Liu. Utilizing Specification Testing in Review Task Trees for Rigorous Review of Formal Specifications. In Proceedings of 10th Asia-Pacific Software Engineering Conference (APSEC03), Chiangmai, Thailand, December 10–12 2003. IEEE Computer Society Press.

#### **Tutorial: Software Model Checking**

Edmund Clarke1 and Daniel Kroening2,\*

**Abstract.** Model Checking is an automated technique for the systematic exploration of uthe state space of a state transition system. The first part of the tutorial provides an introduction to the basic concepts of model checking, including BDD-and SAT-based symbolic model checking, partial order reduction, abstraction, and compositional verification. Model Checking has been applied successfully to hardware in the past. However, software has become the most complex part of safety ciritcal systems. The second part of the tutorial covers tools that use Model Checking to formally verify computer software.

#### 1 Introduction

Software has become the most complex part of today's safety critical embedded systems. Testing methods can only provide very limited coverage due to the enormous state space that needs to be searched. Formal verification tools, on the other hand, promise full coverage of the state space. Introduced in 1981, *Model Checking* [1, 2] is one of the most commonly used formal verification techniques in a commercial setting. The first part of the tutorial reviews classical explicit state and symbolic model checking algorithms with a focus on software.

The capacity of Model Checking algorithms is constrained by the state-space explosion problem. In case of BDD-based symbolic model checking algorithms, this problem manifests itself in the form of unmanagbly large BDDs. Thus, techniques to reduce the size of the state space, such as the partial order reduction, are discussed.

Abstraction and compositional verification techniques will also be covered briefly. The second part of the tutorial discusses tools and algorithms for the model checking computer software. We first cover explicit state methods and implementations such as Spin, JPF [3], Bogor [4], and CMC [5]. We describe the area of application of each of

Department of Computer Science, Carnegie Mellon University, Pittsburgh, PA, 15213

<sup>&</sup>lt;sup>2</sup> Computer Systems Institute, ETH Zürich, Switzerland

<sup>\*</sup> This research was sponsored by the Gigascale Systems Research Center (GSRC), the National Science Foundation (NSF) under grant no. CCR-9803774, the Office of Naval Research (ONR), the Naval Research Laboratory (NRL) under contract no. N00014-01-1-0796, and by the Defense Advanced Research Projects Agency, and the Army Research Office (ARO) under contract no. DAAD19-01-1-0485, and the General Motors Collaborative Research Lab at CMU. The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of GSRC, NSF, ONR, NRL, DOD, ARO, or the U.S. government.

J. Davies et al. (Eds.): ICFEM 2004, LNCS 3308, pp. 9-10, 2004.

these tools using a concrete example. However, the size of the software system is usually severely constrained when using explicit state model checker.

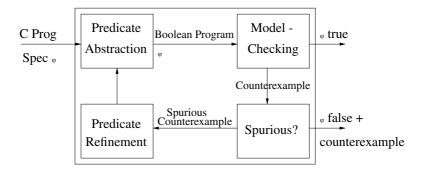

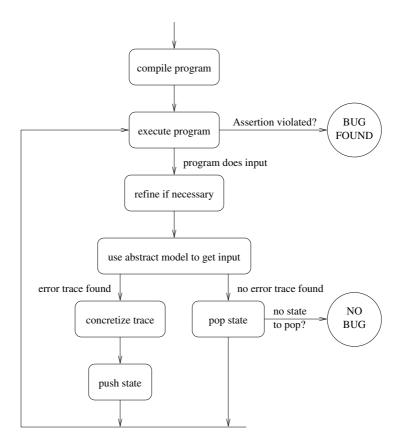

Software model checking has, in recent years, been applied successfully to large, real software programs, but within certain restricted domains. Many of the tools that have been instrumental in this success have been based on the Counterexample Guided Abstraction Refinement (CEGAR) paradigm [6, 7], first used to model check software programs by Ball and Rajamani [8]. Their SLAM tool [9] has demonstrated the effectiveness of software verification for device drivers. BLAST [10] and MAGIC [11] have been applied to security protocols and real-time operating system kernels.

A common feature of the success of these tools is that the programs and properties examined did not depend on complex data structures. The properties that have been successfully checked or refuted have relied on control flow and relatively simple integer variable relationships. SLAM, BLAST, and MAGIC rely on theorem provers to perform the critical refinement step. The tutorial covers some of the details of these implementations.

#### References

- 1. E. Clarke, O. Grumberg, and D. Peled. *Model Checking*. MIT Press, 2000.

- E. M. Clarke and E. A. Emerson. Synthesis of synchronization skeletons for branching time temporal logic. In *Logic of Programs: Workshop*, volume 131 of *LNCS*. Springer-Verlag, 1981.

- 3. W. Visser, K. Havelund, G. Brat, S. Park, and F. Lerda. Model checking programs. *Automated Software Engineering*, 10(2):203–232, 2003.

- 4. Robby, E. Rodriguez, M. Dwyer, and J. Hatcliff. Checking strong specifications using an extensible software model checking framework. In *Tools and Algorithms for the Construction and Analysis of Systems*, pages 404–420, 2004.

- M. Musuvathi, D. Park, A. Chou, D. Engler, and D. Dill. CMC: a pragmatic approach to model checking real code. In *Symposium on Operating System Design and Implementation*, 2002.

- R. P. Kurshan. Computer-Aided Verification of Coordinating Processes: The Automata-Theoretic Approach. Princeton University Press, 1995.

- 7. E. Clarke, O. Grumberg, S. Jha, Y. Lu, and H. Veith. Counterexample-guided abstraction refinement. In *Computer Aided Verification*, pages 154–169, 2000.

- 8. T. Ball and S.K. Rajamani. Boolean programs: A model and process for software analysis. Technical Report 2000-14, Microsoft Research, February 2000.

- 9. T. Ball and S. Rajamani. Automatically validating temporal safety properties of interfaces. In *SPIN Workshop on Model Checking of Software*, pages 103–122, 2001.

- 10. T. A. Henzinger, R. Jhala, R. Majumdar, and G. Sutre. Lazy abstraction. In *Principles of Programming Languages*, pages 58–70, 2002.

- 11. S. Chaki, E. Clarke, A. Groce, S. Jha, and H. Veith. Modular verification of software components in C. *IEEE Transactions on Software Engineering*, 30(6):388–402, June 2004.

#### **Engineering Quality Software**

Amitabh Srivastava

Microsoft Corporation

Producing high performing, reliable and secure software is a challenging problem in the software industry. An important element in achieving this goal lies in the automation of the software development process, which currently is primarily manual. However, progress in program specification, verification, and testing is more rapid today than ever before. At Microsoft, we have developed innovative techniques to address some of these challenges. Our techniques scale to meet the requirements of real production environments and span the whole development process from software architecture to sustained engineering. These methodologies are making huge impact in the development of Windows and other products at Microsoft. This talk focuses on the challenges in software development, describes our progress and experience, and outlines remaining problems.

### When Can Formal Methods Make a Real Difference?

Peter G. Neumann

SRI International Computer Science Lab, Menlo Park, CA 94025 Neumann@CSL.sri.com http://www.csl.sri.com/neumann

This talk will consider a few cases from the ACM Risks Forum archives

http://www.risks.org

for which the sensible use of formal methods could have made a decisive difference in avoiding serious consequences — with respect to requirements, specifications, human interfaces, implementation, and even operation, typically in systems that were supposedly safe, reliable, or secure. This will provide a view to the future in terms of things we can learn about the past.

#### On the Adoption of Formal Methods by Industry: The ACL2 Experience

#### J Strother Moore

Department of Computer Sciences, University of Texas at Austin

Formal methods are gradually being adopted by industry. The complexity of industrial designs – often seen as an impediment to the use of formal methods – is actually one of the main arguments in favor of mechanized formal methods. No other tool is as good as mechanized mathematical modeling at capturing the complexity and giving the human designers the facilities for explaining the reasons their designs are correct and controlling the revelation of the relevant complexity.

In this talk I will describe the ongoing Boyer-Moore project, which for three decades has been concerned with the use of mechanized theorem proving to verify properties of hardware and software. The current theorem prover, ACL2, is the product of Matt Kaufmann and the speaker, and has been used to verify

- the correspondence of a bit- and cycle-accurate micro-architectural model of a Motorola digital signal processor and the microcode engine it implemented,

- the verification of some microcode for that Motorola dsp,

- the correctness, with respect to the IEEE 754 floating point standard, of the AMD K5's FDIV and FSQRT instructions,

- the correctness of the RTL implementing the elementary floating point operations on the AMD Athlon and other AMD fpu designs,

- process isolation properties of the microcode implementing a separation kernel on the Rockwell AAMP7 processor, and

- properties of JVM bytecode and of the JVM itself, including ongoing work on the bytecode verifier and class loader.

I will sketch how we got to this state of affairs and some of the key reasons ACL2 has been adopted for these and other projects.

#### A CLP Approach to Modelling Systems

Joxan Jaffar\*

School of Computing, National University of Singapore, Republic of Singapore 117543

We present a formal method for modelling the operational behavior of various kinds of systems of concurrent processes. A first objective is that the method be broadly applicable. A system can be described in terms of its processes written in a traditional syntax-based manner, or in some non-traditional form such as a timed automaton. The number of processes may be fixed, or parameterized, or, because of dynamic process creation, unbounded. The communication and synchronization between processes may be synchronous or not, and via shared variables or some form of channels. We may have a traditional interleaving of processes, or use a specific scheduling strategy. The observables modelled should not be restricted to just the values of the program variables, but possibly other attributes of the system such as its registers and cache, its clock and battery values, etc. An example application area which touches upon these characteristics is that of determining worst-case execution time.

We choose to model a generic system S in the form of a CLP program P. The model-theoretic semantics of P shall characterize the "collecting" semantics of S, that is, those states that are observable. The proof-theoretic semantics of P, on the other hand, further characterize the "trace" semantics of S. An advantage of this CLP approach is that intricate details of the system can be captured in a familiar logical framework.

We then present a specification language for an extensive class of system behaviors. In addition to the traditional safety and liveness properties which specify the universality or eventuality of certain predicates on states, we introduce the notions of *relative safety* and *relative progress*. The former extends traditional safety assertions to accommodate non-behavioral properties such as symmetry, serializability and commutativity between processes. The latter provides for specifying progress properties. Our specification method is not just for stating the property of interest, but also for the *assertion* of properties held at various program points.

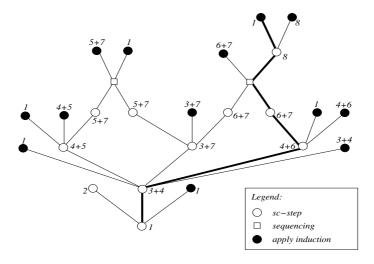

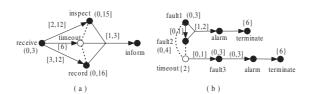

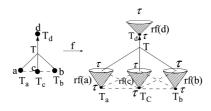

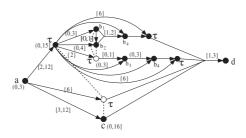

Finally, we present an inference method, based upon a notion of  $inductive\ tabling$ , for proving an assertion A. This method can use assertions that have already been proven, use the assertion A itself, in a manner prescribed by induction principles, and dynamically generate new assertions. All these properties are shown to be useful in preventing redundant computations, which then can lead to efficient proofs. Our proof method thus combines the search characteristic of model-checking and abstract interpretation, and methods of inductive assertions. We demonstrate a prototype implementation on some benchmark examples.

<sup>\*</sup> Joint work with Andrew Santosa and Răzvan Voicu

J. Davies et al. (Eds.): ICFEM 2004, LNCS 3308, p. 14, 2004.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2004

#### **Multi-prover Verification of C Programs**

Jean-Christophe Filliâtre and Claude Marché

\*PCRI — LRI (CNRS UMR 8623) — INRIA Futurs — Université Paris 11, Bât 490, Université Paris-sud, 91405 Orsay cedex, France

**Abstract.** Our goal is the verification of C programs at the source code level using formal proof tools. Programs are specified using annotations such as pre- and post-conditions and global invariants. An original approach is presented which allows to formally prove that a function implementation satisfies its specification and is free of null pointer dereferencing and out-of-bounds array access. The method is not bound to a particular back-end theorem prover. A significant part of the ANSI C language is supported, including pointer arithmetic and possible pointer aliasing. We describe a prototype tool and give some experimental results.

**Keywords:** C programming language, Hoare logic, pointer programs, formal verification and proof.

#### 1 Introduction

Using formal methods for verifying properties of programs at their source code level has gained more interest with the increased use of embedded programs, which are short programs where a high-level of confidence is required. Such embedded programs are no more written in assembly language but in C (plane command control, cars, etc.) or in JavaCard [21] (mobile phones, smart cards, etc.). This paper introduces a verification method for ANSI C source code, following the same approach as the one we used for Java [15, 16]. A prototype tool has been implemented, called Caduceus, freely available for experimentation [11]. This tool is currently under experimentation at Axalto (smart cards) and Dassault Aviation (aeronautics).

In the following, we assume the reader fairly familiar with ANSI C [13]. In our setting, the properties that may be checked are of two kinds: first, the program may be checked to be free of *threats* (null pointer dereferencing or out-of-bounds array access) and second, it may be proved satisfying functional properties given as functions's *postconditions*. These kinds of properties are not independent since they both usually need insertion of appropriate annotations (functions's *preconditions*, *global invariants*, *loop invariants*, etc.) as usual in a Hoare logic framework. In practice, these annotations are inserted in the source code as comments of a specific shape /\*@...\*/. The specification language we use in those comments is largely inspired by the Java Modeling Language (JML) [14]. It has however significant differences, mainly due to the fact that unlike JML we do not seek runtime assertion checking.

<sup>\*</sup> This research was partly supported by the "projet GECCOO de l'ACI Sécurité Informatique", CNRS & INRIA, http://gecco.lri.fr.

J. Davies et al. (Eds.): ICFEM 2004, LNCS 3308, pp. 15-29, 2004.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2004

Once a C program is annotated, verification is done by running Caduceus on the sources in a way similar to a classical compiler but resulting in the generation of the so-called *verification conditions*: these are first-order predicate logic formulas whose validity implies the soundness of the program with respect to the absence of threat and to the functional properties given as annotations. At this point, a general purpose theorem prover must be used to establish those verification conditions. An original Caduceus feature is its independence with respect to the prover. It currently supports the Coq interactive proof assistant [7] and the Simplify automatic prover [1]. New provers may easily be added provided a suitable pretty-printer; support for PVS [18] and haRVey [19] are planned in a near future.

A significant part of ANSI C is supported. All control structures are supported except goto. Pointer programs are supported, including pointer arithmetics and possible pointer aliasing, using old ideas from Burstall [4] recently emphasized by Bornat [3] and used for a case study by Mehta and Nipkow [17]. The main unsupported feature is the cast of pointer (e.g. when pointers to void are used to write "polymorphic" functions).

In this paper we present both an overview of Caduceus from a user's point of view and the method used internally to generate the verification conditions. This method is very similar to the one we used for Java programs and a significant amount of work is shared: the generation of the conditions is indeed realized by a common intermediate tool called Why [9, 10] whose input language—also annotated with Hoare-like preand postconditions—is specifically designed for the purpose of verification conditions generation. In other words, Caduceus is a compiler from annotated C programs to the Why input language.

We seek for a method which guarantees soundness with the highest level of confidence, even if it is not fully automatic. In other words, our approach differs from static checking methods, which are always fully automated but may sometimes miss bugs.

This paper is organized as follows. Section 2 gives an overview of the use of Caduceus with a presentation of the specification language, examples and experimental results. In Section 3, we describe the internal approach used to perform verification, including the modeling of heap memory, the translation to Why and discussion about soundness. We conclude in Section 4 with a comparison to related works.

#### 2 Overview of Caduceus and Its Specification Language

This section gives an overview of Caduceus from a user's point of view based on small examples. A comprehensive description of the annotation syntax can be found in the Caduceus reference manual [11].

#### 2.1 A Simple Character Queue

We start with a very simple C program implementing a character queue within a circular array. The queue is a global structure q declared on Figure 1. The array q.contents contains the queue elements stored from index q.first included to index q.last excluded. q.length is the length of q.contents, that is the maximal capacity of the queue. The boolean fields q.empty and q.full indicate whether the queue is empty or full respectively.

```

struct queue {

char *contents;

int length;

int first, last;

unsigned int empty, full :1;

} q;

```

Fig. 1. A character queue within a circular array

It is natural to associate an invariant to such a global declaration. It avoids repeating the same properties in all functions's specifications. For instance, we may declare that q.contents points to a valid (i.e. allocated) array of at least q.length elements and that q.first and q.last are valid indexes within this array. This is done using the global declaration invariant as follows:

```

/*@ invariant q_invariant :

@ \valid_range(q.contents, 0, q.length-1) &&

@ 0 <= q.first < q.length &&

@ 0 <= q.last < q.length

@*/</pre>

```

Informally, such an invariant is added to the precondition of each function involving q and to the postcondition of each function possibly modifying q. The precise meaning of "involving" and "possibly modifying" is given below.

Annotations such as the above invariant are first-order logic predicates built from atoms and connectives such as &&, | |, !, etc. Atoms are built from side-effects free C expressions and predicate symbols. Here, \valid\_range is a predefined predicate expressing that a given array range can be safely dereferenced.

A function specification is given right before the function definition and is composed of three (optional) clauses: a precondition introduced by the keyword requires, a side-effects clause introduced by the keyword assigns and a postcondition introduced by the keyword ensures. For instance, here is a possible specification/definition of a function push adding an element in q:

```

/*@ requires !q.full

@ assigns q.empty, q.full, q.last, q.contents[q.last]

@ ensures !q.empty && q.contents[\old(q.last)] == c

@*/

void push(char c) {

q.contents[q.last++] = c;

if (q.last == q.length) q.last = 0;

q.empty = 0;

q.full = (q.first == q.last);

}

```

The requires clause is a predicate that must hold whenever the function is called; here it states that q must not be full.

The assigns clause indicates the set of locations possibly modified by the function call. More precisely, it says that any memory location already allocated before the function call and not mentioned in this set is left untouched by the function call.

The ensures clause is a predicate that must hold whenever the function returns. Values of expressions or predicates in the prestate—the program point corresponding to the function call—can be obtained using the \old() modifier. For instance we write here \old(q.last) to denote the value of q.last when push was called.

When run on the above code, Caduceus produces several verification conditions expressing that (1) the postcondition and the assigns clause of push are established, (2) the invariant q\_invariant is preserved by push, and (3) the code of push contains no null pointer dereference (which means here that the assignment of q.contents[q.last++] is valid).

To establish the validity of these conditions, a theory (i.e. a set of axioms) is provided (see Section 3.4). Using the Simplify decision procedure with this theory, the three conditions for push are automatically discharged. With the Coq proof assistant, proofs are easily handled (6 lines of tactics to write).

A function specification can also be attached to a function declaration, this function being defined later or not. For instance we can declare a pop function together with its specification:

```

/*@ requires !q.empty

@ assigns q.empty, q.full, q.first

@ ensures !q.full && \result == q.contents[\old(q.first)]

@*/

char pop();

```

Notice, in the postcondition, the use of \result to denote the returned value.

It is important to notice that our verification process is modular, in the sense that when another function calls push or pop, only their specifications are seen. In other words the implementation of push may be changed or the one of pop added without affecting the remaining of the verification process. Notice also that the assigns clauses are essential for modularity of the verification, not only because they specify what is modified, but mainly because they specify that everything else is unmodified (see Section 3.4).

#### 2.2 In-place List Reversal

We continue with a now classical example: in-place list reversal [3, 4, 17]. The code is given Figure 2. It introduces a type list for linked list of integers and a function reverse that reverses a list in-place.

To write a specification for reverse we first need to express that the list p0 is finite. This cannot be expressed using a first-order predicate (assuming no primitive). A solution could have been to allow the use of side-effect free functions from the code itself, like in JML for instance. This would clearly make sense for runtime assertion checking, but for formal verification we think it is better to clearly separate the code side and the logic side. So instead, in our setting predicates and logical functions required to write specifications must be defined on the logic side, that is in the language of the backend theorem prover, and imported into the source code.

```

typedef struct struct_list {

int hd;

struct struct_list *tl;

} *list;

list reverse(list p0) {

list r = p0, p = NULL;

while (r != NULL) {

list q = r;

r = r->tl; q->tl = p; p = q;

}

return p;

}

```

Fig. 2. In-place list reversal

For this example, we import a predicate is\_list, supposed to characterize finite lists, with the following declaration:

```

/*@ predicate is_list(list 1) reads 1->t1 */

```

The clause reads indicates the memory locations involved in the predicate definition. This is indeed mandatory for the predicate to be applied to the corresponding variables on the logic side. On this example, the definition of is\_list obviously requires the knowledge of the tl fields of lists cells.

We need additional predicates to give reverse a postcondition. Indeed we must relate the returned list to the input list. Following [17] we introduce a predicate llist relating a C list p (a pointer) to the list of all its elements:

```

/*@ predicate llist(list p, plist l) reads 1->tl */

```

Here plist is an abstract type of pointer lists defined on the logic side. With the additional declaration of a reverse function on type plist

```

/*@ logic plist rev(plist pl) */

```

it is then possible to write a specification for reverse:

```

/*@ requires is_list(p0)

@ ensures \forall plist 10;

@ \old(llist(p0, 10)) => llist(\result, rev(10)) @*/

list reverse(list p0) { ...

```

It is important to note that the function symbol rev involved in the specification is not at all related to the C function reverse being defined.

As usual with Hoare-like annotations, we need to annotate the loop to be able to prove function reverse correct. We insert a loop invariant and a variant to ensure the termination, respectively introduced by the keywords invariant and variant:

```

/*@ invariant

\exists plist lp; \exists plist lr;

llist(p, lp) && llist(r, lr) && disjoint(lp, lr) &&

\forall plist l;

\old(llist(p0, l)) => app(rev(lr), lp) == rev(l)

```

```

@ variant length(r) for length_order */

while (r != NULL) { ...

```

The invariant involves new importations:

```

/* app(11,12) is the concatenation of 11 and 12 */

/*@ logic plist app(plist 11, plist 12) */

/* disjoint(11,12) is true whenever 11 and 12 have no element in common */

/*@ predicate disjoint(plist 11, plist 12) */

```

and the variant also requires importations of length and length.order (see [11] for details).

With these annotations, Caduceus generates 7 verification conditions for the C function reverse. The Simplify prover only established 4 of them automatically, which is not surprising because indeed we did not provide a full theory for the new predicates such as llist. On the other hand, we defined in Coq a model for these predicates using the predefined Coq lists and all conditions have been proved correct. The proofs amount to 70 lines of tactics. The model for linked lists (definition of llist, etc.) is around 180 lines long and is reusable for other programs involving linked lists.

We are currently experimenting Caduceus on the Schorr-Waite algorithm which is considered as a benchmark for pointer programs verification [3, 17]. Compared to the proof in Isabelle/HOL [17], we also check the absence of threats. Since annotations from [17] fit in our specification language, we strongly believe that Isabelle/HOL proofs will be adapted to Coq without difficulty.

#### 3 The Verification Technique

Our approach is to translate annotated C programs into Why's input language. The latter does not provide any data structure, but only applicative types (primitive types such as integers, booleans, etc. and *abstract* datatypes) and mutable variables containing applicative values. This means that Why has absolutely no knowledge of arrays, structures, pointers and memory heap in general, hence our translation mechanism needs to introduce definitions of abstract datatypes to model the memory state of a given C program. Then the semantics of C statements must be translated into Why statements operating on these abstract datatypes. In this section we proceed as follows: first we present Why's input language, then we describe our modeling of memory heaps, then we give the translation rules from C statements to Why's statements, then the background theory and finally we discuss about the soundness of the approach.

#### 3.1 The Why Tool

Unlike usual approaches in Hoare logic, Why's core language is not Pascal-like but ML-like: there is no difference between expressions and statements (the latter are simply expressions of type unit, which is similar to void in C) and immutable variables are introduced by let..in.. constructs. On top of this side-effect free core language, modifiable variables are introduced using an explicit reference type ref as in SML or

OCaml. A feature of great importance for us is that Why rejects any variable aliasing (rejecting aliasing is required by Why to guarantee the soundness of verification condition generation), hence dealing with pointer programs requires an appropriate modeling of memory. Finally, beside usual imperative control statements (sequence, conditional and while loops) Why features exceptions with a try-catch mechanism. Exceptions will be used to encode return, break and continue C statements.

Why programs can be annotated using pre- and postconditions, loop invariants and intermediate assertions. Logical formulas are written in a (possibly polymorphic) typed first-order logic with built-in equality, booleans, infinite precision integers and real numbers with usual operations. Why performs an *effect analysis* (see below) on modifiable variables of programs, a classical weakest precondition computation [8] and generates proof obligations for various provers.

Why has a modular approach. New logic functions or predicate symbols can be introduced and freely used in the specification part. Sub-programs can also be introduced abstractly, by the mean of a full specification: type of input variables and result, pre- and postconditions, as well as its *effects*, that is the sets of global references possibly read and/or written by the subprogram.

In order to translate an annotated C program into Why, one needs to proceed the following way:

- 1. Find an appropriate modeling of C memory states using global Why variables which will never be aliased:

- 2. Translate C constructs into Why statements, with assignments over the global variables introduced above;

- 3. Translate annotations into Why predicates over those variables.

Because C functions can be mutually recursive, we first give a specification for all the functions as abstract Why subprograms with specifications. This abstract view is used to interpret function calls and suffices to ensure partial correctness of programs.

Figure 3 shows the Why abstract declaration of the subprogram corresponding to the push function of Section 2.1. It has one argument (the integer c) which is supposed to satisfy the precondition (first formula between curly braces). There is no result (output type is unit), it accesses nine global variables (listed after **reads**) and writes four (listed after **writes**). The postcondition (second pair of curly braces) uses the notation x@ to denote the value of variable x before the function application. The predicates valid, valid\_range and assigns, and function symbols acc, shift and pointer\_loc are easily understood as translation of specifications; they are formally introduced in the next sections.

#### 3.2 Modeling C Memory Heap

The C memory is represented by a finite set of Why variables, each containing an applicative map. We adopt Burstall's approach [4], recently emphasized by Bornat [3] then Mehta and Nipkow [17]. The key idea is to have one Why variable for each structure field. Indeed, two structure fields cannot be aliased (as soon as one conforms to ANSI C). The very useful consequence is that whenever one structure field is updated, only the corresponding Why variable is modified and we have for free that any other field is left untouched. We extend this model to arrays and more generally to pointer arithmetic.

```

\begin{array}{l} \textbf{parameter} \  \, \text{pushparameter} : c : \text{int} \rightarrow \\ \left\{ \  \, \text{acc}(full,q) = 0 \land \text{valid}(alloc,q) \land \\ \quad \text{valid\_range}(alloc, \text{acc}(contents,q), 0, \text{acc}(length,q) - 1) \land \\ \quad 0 \leq \text{acc}(first,q) < \text{acc}(length,q) \land 0 \leq \text{acc}(last,q) < \text{acc}(length,q) \right\} \\ \text{unit} \  \, \textbf{reads} \  \, alloc, contents, empty, first, full, intP, last, length, q \\ \quad \textbf{writes} \  \, empty, full, intP, last \\ \left\{ \  \, \text{acc}(empty,q) = 0 \land \text{acc}(intP, \text{shift}(\text{acc}(contents,q), \text{acc}(last@,q@))) = c \land \\ \quad \text{assigns}(alloc@, last@, last, \text{pointer\_loc}(q@)) \land \\ \quad \text{assigns}(alloc@, intP@, intP, \\ \quad \quad \text{pointer\_loc}(\text{shift}(\text{acc}(contents@,q@), \text{acc}(last@,q@)))) \land \\ \quad \text{assigns}(alloc@, full@, full, \text{pointer\_loc}(q@)) \land \\ \quad \text{assigns}(alloc@, empty@, empty, \text{pointer\_loc}(q@)) \land \\ \quad \text{valid\_range}(alloc, \text{acc}(contents,q), 0, \text{acc}(length,q) - 1) \land \\ \quad 0 \leq \text{acc}(first,q) < \text{acc}(length,q) \land 0 \leq \text{acc}(last,q) < \text{acc}(length,q) \right\} \end{array}

```

Fig. 3. Why interpretation of push

Fig. 4. Modeling of C memory heap

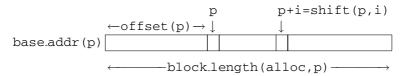

The set of variables representing the C memory is displayed on Figure 4. All these variables contain applicative maps indexed by addresses  $a_1, a_2, \ldots$  belonging to some abstract data type addr. The variable alloc on the left of the figure is the *allocation store* which tells for each address whether it is allocated and, when so, the size of the block it points to. All other variables map addresses to 1-dimensional arrays indexed by integers. A type pointer is introduced to represent C pointers. A value of type pointer is either the null pointer or a pair of an address and an integer index. For instance, address  $a_2$  points to a block of length 5 according to alloc and thus the pointer  $(a_2,3)$  refers to the fourth element of each array  $f_1(a_2), f_2(a_2), \ldots$  The variable intP is used for arrays of integers i.e. pointers to int, intPP for pointers to pointers to int, etc. Similarly the variable pointerP is used for pointers to structures, pointerPP for pointers to pointers to structures, etc.

On the Why side, each of those applicative maps is of type  $\alpha$  memory, an abstract polymorphic datatype equipped with the following side-effect free functions, to access a cell and to update it, respectively.

```

acc: \alpha memory, pointer \rightarrow \alpha upd: \alpha memory, pointer, \alpha \rightarrow \alpha memory

```

Depending on the memory used,  $\alpha$  is either int, float or pointer. We also introduce one Why variable for each C global variable or static local variable. Finally, C local variables are represented using Why local variables since they cannot be aliased.

**Effects Inference.** Once we have determined the set of variables representing the memory state, a non-trivial step to be able to deal modularly with function calls is to statically compute the *effects* of each statement and each function. An effect is a pair of sets of Why variables respectively (possibly) accessed and modified. Such an effect appears on Figure 3 (the **reads** and **writes** clauses).

Computing statements effects is straightforward: it is only a matter of traversing statements and expressions recursively, collecting accessed and modified variables along and assuming known effects for all functions. Computing functions effects is then obtained by iterating effects inference on each function body until a fixpoint is reached, which is guaranteed to happen since the set of variables is finite and effects can only grow during this process.

### 3.3 Translating C Source Code

This section describes the translation from C source code to Why source code. The translation is realized through four mutually recursive interpretations:

- [e]: the interpretation of a C expression e;

- [[e]]<sub>b</sub>: the interpretation of a C expression e as a Why boolean expression—though C does not have booleans, the translation is more natural when a C expression e used as a boolean is directly translated into a Why boolean;

- $[e]_l$ : the interpretation of a C *left value* e, i.e. an expression allowed on the left of an assignment;

- [s]: the interpretation of a C statement s.

**Left Values.** The interpretation of a left value e is either a Why reference x or a pair (m,p) of a memory m and a pointer expression p. This interpretation is defined as follows:

```

- \ \llbracket x \rrbracket_l = x \\ - \ \llbracket \star e \rrbracket_l = (m, \llbracket e \rrbracket), \text{ where } m \text{ depends on the type of } e, \text{e.g. intP for int} \star, \text{intPP for int} \star, \text{etc.} \\ - \ \llbracket e -> f \rrbracket_l = (f, \llbracket e \rrbracket)

```

**Expressions.** We only give the most significant constructs. Translation of memory access and assignment is done via two abstract Why programs

```

\begin{array}{l} \textbf{parameter} \ \texttt{access} : m : \alpha \ \texttt{memory} \ \texttt{ref} \rightarrow p : \texttt{pointer} \rightarrow \\ \{\texttt{valid}(alloc,p)\} \ \alpha \ \textbf{reads} \ alloc, m \ \{result = \texttt{acc}(m,p)\} \\ \\ \textbf{parameter} \ \texttt{update} : m : \alpha \ \texttt{memory} \ \texttt{ref} \rightarrow p : \texttt{pointer} \rightarrow v : \alpha \rightarrow \\ \{\texttt{valid}(alloc,p)\} \ \texttt{unit} \ \textbf{reads} \ alloc, m \ \textbf{writes} \ m \ \{m = \texttt{upd}(m@,p,v)\} \\ \end{array}

```

where valid(alloc, p) expresses that p can be safely dereferenced according to alloc. The precise meaning of valid is given Section 3.4.

```

- \|x\| = !x \\ - \|*e\| = \operatorname{access} m \ p, \text{ when } \|*e\|_l = (m,p) \\ - \|e-f\| = \operatorname{access} f \ \|e\| \\ - \|x = e_2\| = x := \|e_2\|; \ !x \\ - \|e_1 = e_2\| = \operatorname{let} v_1 = p_1 \text{ in let } v_2 = \|e_2\| \text{ in update } m \ v_1 \ v_2; \ v_2, \\ \text{when } \|e_1\|_l = (m,p_1) \\ - \|e_1 + e_2\| = \operatorname{shift} \|e_1\| \|e_2\|, \text{ when } e_1 \text{ is a pointer} \\ - \|e_1 \ op \ e_2\| = \|e_1\| \ op \ \|e_2\|, \text{ with } op \in \{+,-,*,/,\$,\&,^{\,},|\,\} \\ - \|e_1 \ op \ e_2\| = \operatorname{if} \|e_1 \ op \ e_2\|_b \text{ then } 1 \text{ else } 0, \\ \text{with } op \in \{==,!=,>,>=,<,=,\&\&,|\,|\,\} \\ - \|f \ (e_1,\dots,e_n)\| = \operatorname{f.parameter} (\|e_1\|,\dots,\|e_n\|)

```

**Boolean Expressions.** The interpretation of a "boolean" expression is defined as follows:

**Statements.** The translation of a C statement is defined as follows:

```

\begin{split} - & \ \llbracket e \rrbracket = \mathtt{let} \ . = \ \llbracket e \rrbracket \ \mathtt{in} \ \mathtt{void} \\ - & \ \llbracket e_1 \ ; \ e_2 \rrbracket = \ \llbracket e_1 \rrbracket \ ; \ \llbracket e_2 \rrbracket \\ - & \ \llbracket \left\{ \ \beta_1 \ \mathtt{x}_1 = e_1 \ ; \ \ldots \ \beta_n \ \mathtt{x}_n = e_n \ ; \ s \ \right\} \right\rrbracket \\ & = \mathtt{let} \ \mathtt{x}_1 = \ \mathtt{ref} \ \llbracket e_1 \rrbracket \ \mathtt{in} \ \ldots \ \mathtt{let} \ \mathtt{x}_n = \ \mathtt{ref} \ \llbracket e_n \rrbracket \ \mathtt{in} \ \llbracket s \rrbracket \end{aligned}

```

The translation above assumes that each variable  $x_i$  has an initializer  $e_i$ . If a local variable has no initializer, it is indeed initialized using a call to an unspecified function, thus simulating a random initialization.

```

- [\![for(e_1;e_2;s_3)\ s]\!] = [\![e_1]\!]; try while [\![e_2]\!] do try [\![s;s_3]\!] with Continue -> void end done with Break -> void end

```

A similar translation is used for while and do loops.

-  $[return e]_s = raise (Return <math>[e]$ )

Finally, a C function definition is interpreted as a Why function definition where the exception Return is caught appropriately: